# NRC Publications Archive Archives des publications du CNRC

## Monolithic integration of AlGaN/GaN HFET with MOS on silicon<111>substrates

Chyurlia, P. N.; Semond, F.; Lester, T.; Bardwell, J. A.; Rolfe, S.; Tang, H.; Tarr, N. G.

This publication could be one of several versions: author's original, accepted manuscript or the publisher's version. / La version de cette publication peut être l'une des suivantes : la version prépublication de l'auteur, la version acceptée du manuscrit ou la version de l'éditeur.

For the publisher's version, please access the DOI link below./ Pour consulter la version de l'éditeur, utilisez le lien DOI ci-dessous.

#### Publisher's version / Version de l'éditeur:

https://doi.org/10.1049/el.2010.3167 Electronics Letters, 46, 3, 2010-02-04

#### NRC Publications Record / Notice d'Archives des publications de CNRC:

https://nrc-publications.canada.ca/eng/view/object/?id=37196b3c-a04d-42fb-b33f-d789a510f798 https://publications-cnrc.canada.ca/fra/voir/objet/?id=37196b3c-a04d-42fb-b33f-d789a510f798

Access and use of this website and the material on it are subject to the Terms and Conditions set forth at <a href="https://nrc-publications.canada.ca/eng/copyright">https://nrc-publications.canada.ca/eng/copyright</a>

READ THESE TERMS AND CONDITIONS CAREFULLY BEFORE USING THIS WEBSITE.

L'accès à ce site Web et l'utilisation de son contenu sont assujettis aux conditions présentées dans le site <a href="https://publications-cnrc.canada.ca/fra/droits">https://publications-cnrc.canada.ca/fra/droits</a>

LISEZ CES CONDITIONS ATTENTIVEMENT AVANT D'UTILISER CE SITE WEB.

#### Questions? Contact the NRC Publications Archive team at

PublicationsArchive-ArchivesPublications@nrc-cnrc.gc.ca. If you wish to email the authors directly, please see the first page of the publication for their contact information.

Vous avez des questions? Nous pouvons vous aider. Pour communiquer directement avec un auteur, consultez la première page de la revue dans laquelle son article a été publié afin de trouver ses coordonnées. Si vous n'arrivez pas à les repérer, communiquez avec nous à PublicationsArchive-ArchivesPublications@nrc-cnrc.gc.ca.

### Monolithic integration of AlGaN/GaN HFET with MOS on silicon (111) substrates

P.N. Chyurlia, F. Semond, T. Lester, J.A. Bardwell, S. Rolfe, H. Tang and N.G. Tarr

AlGaN/GaN HFETs and silicon MOSFETs have been integrated monolithically on a silicon  $\langle 111 \rangle$  substrate. A differential heteroepitaxy technique was used to grow AlGaN/GaN HFET layers on silicon  $\langle 111 \rangle$  substrates while leaving protected areas of atomically smooth silicon in which MOSFETs are built.

Introduction: AlGaN/GaN heterostructure field effect transistors (HFETs) have attracted much attention in recent years owing to their high breakdown voltage and high temperature operation capability compared to transistors in other material families. However, existing AlGaN/GaN HFET technologies tend to be poorly suited to integration of digital or mixed-signal circuits, limiting the applications of these devices. This Letter reports the first monolithic integration of AlGaN/ GaN HFETs with silicon MOSFETs using differential heteroepitaxy on (111) silicon substrates [1]. Integrating both technologies allows for an expanded set of applications that can take advantage of the high voltage and high power handling capability of AlGaN/GaN HFETs as well as the high density, simplicity and low power consumption of MOS digital circuitry. An example of such an application would be to integrate CMOS DSP circuitry with a GaN-based power amplifier for transmit modules in wireless telecom systems. This would extend the work of Matsunaga et al. who used a hybrid chip which combines a class-B GaN PA with a CMOS circuit to provide dynamic biasing in order to improve linearity and efficiency [2]. Additionally there is great interest in GaN-based chemical, gas, biological, pressure and mass sensors [3, 4]. This work opens the door for the integration of MOS devices along with a GaN-based sensor, allowing for compact, low power read-out circuitry. An alternative hybrid approach to AlGaN/GaN HFET integration with CMOS was reported recently by Chung et al. [5].

Device fabrication: Decomposition of the GaN material system during the high thermal budget required in MOS processing, particularly during thermal oxidations (field and gate oxide) and implant annealing, is the primary obstacle to be overcome in accomplishing monolithic HFET/MOS integration. Fortunately CMOS thermal budgets have been reduced drastically in recent years through the adoption of techniques such as implanted retrograde wells, shallow trench isolation (STI) and even gate dielectric deposition. Integration here was based on relatively old MOS technology with 25 nm thermal gate oxide. Since STI was not available, enclosed geometry MOSFETs were used to avoid the thermal budget required for thick field oxide growth.

AlGaN/GaN layers were grown by ammonia-MBE on 50 mm diameter  $10k\Omega$ cm silicon  $\langle 111 \rangle$  substrates using the windowed growth technique described in detail in [6]. It should be possible to scale the growth technique to the much larger silicon wafer diameters used in commercial CMOS [7]. The GaN stack consists of alternating AlN and GaN stress relief layers followed by a 1.4 µm C-doped semi-insulating GaN buffer, a 200 nm undoped GaN channel layer and a 20 nm Al<sub>0.3</sub>Ga<sub>0.7</sub>N cap. Areas in which MOSFETs were to be formed were protected by a 1.8 µm PECVD silicon dioxide layer overlaid with 100 nm sputtered a-Si during AlGaN/GaN layer growth. MOSFET areas were then selectively exposed by wet chemical etching of the PECVD silicon dioxide, lifting off the a-Si and overgrown GaN layers. To obtain useful MOSFET threshold voltages and avoid short channel effects silicon doping in the near-surface region was increased by a series of <sup>11</sup>B<sup>+</sup> ion implants to form a retrograde well. The 25 nm thermal gate oxide was then grown at 900°C in dry oxygen, followed by a 900°C nitrogen anneal to reduce oxide fixed charge. Undoped polysilicon was then deposited by LPCVD at 625°C and etched in CF<sub>4</sub>/O<sub>2</sub> plasma to define gate electrodes. Source/drain regions were formed by diffusion from a POCl<sub>3</sub> source for 30 min at 900°C giving a sheet resistance of 33  $\Omega$ /square. A borophosphosilicate glass (BPSG) layer was then deposited to protect the MOSFETs during HFET processing and flowed to smooth surface topography. The total thermal budget for MOSFET formation including BPSG flow was 900°C for 90 min.

HFETs were formed following the process described in [8]. These devices were mesa isolated with chemically assisted ion beam etching

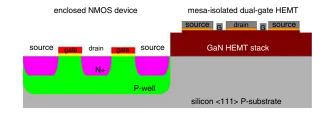

(CAIBE). An evaporated Ti/Al/Ti/Ag stack [9] with HCl pre-treatment was used to form source/drain ohmic contacts. A Pt-based Schottky gate metal was evaporated. It should be noted that gold is not used in the metallisation scheme to avoid minority carrier lifetime degradation and junction leakage in the silicon devices. A cross-section through the completed device structures is shown in Fig. 1.

Fig. 1 Cross-section of integrated devices NMOS device shown on left, mesa-isolated GaN HEMT on right

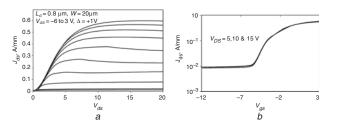

Results: Fig. 2 shows the drain characteristic of a typical HFET with gate length of 0.8  $\mu$ m and width of 40  $\mu$ m. The saturation drain current is 0.45 A/mm for  $V_G=0$ , with a pinch-off voltage of -5 V. Further optimisation of the Ag-based ohmic contact is required and would be expected to result in improved drain currents

Fig. 2 DC I-V characteristic and pinchoff of GaN HEMT device a DC I-V characterictic b Pinchoff  $L_G=0.8~\mu\mathrm{m},~W_G=80~\mu\mathrm{m}$

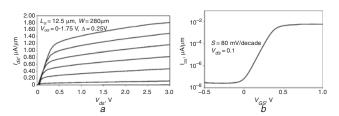

Fig. 3 shows the drain and subthreshold characteristics of a typical MOSFET with length of 12.5  $\mu$ m and width of 280  $\mu$ m. The threshold voltage is approximately 0.3 V, which is consistent with TSuprem simulation. The maximum channel effective electron mobility estimated from the peak transconductance is 498 cm<sup>2</sup>V<sup>-1</sup> s<sup>-1</sup>, indicating that the oxidation process has produced relatively low interface trap densities  $D_{it}$  and that the silicon surface in the window has not been damaged during the AlGaN/GaN layer growth. A subthreshold swing (Fig. 3b) of 80 mV/decade is also measured, confirming low  $D_{it}$ .

Fig. 3 DC I-V characterictic and subthreshold of enclosed NMOS device a DC I-V characterictic b Subthreshold  $L_G=12.5~\mu\text{m},~W_G=280~\mu\text{m}$

The use of a  $\langle 111 \rangle$  substrate is, of course, expected to give higher  $D_{ii}$  than would the  $\langle 100 \rangle$  substrates employed for most CMOS technologies. The use of  $\langle 110 \rangle$  silicon substrates to take advantage of higher carrier saturation velocities than provided by  $\langle 100 \rangle$  material is now being considered for state-of-the-art CMOS technologies. AlGaN/GaN heteroepitaxy has been demonstrated on  $\langle 110 \rangle$  silicon substrates [10], so it is plausible that AlGaN/GaN HFETs could eventually be integrated with advanced CMOS without a significant penalty in MOSFET performance.

Conclusion: The first monolithic integration of AlGaN/GaN HFETs and silicon MOSFETs using heteroepitaxy on a silicon substrate is

reported. Protection of the MOSFET regions with a thick PECVD oxide overlaid with a-Si during growth of the AlGaN/GaN layers combined with thermal budget minimisation during MOS processing are the keys to accomplishing this integration. HFET performance was not compromised by the integration. High channel electron mobilities were obtained in the MOSFETs, evidence of the quality of the silicon surface preserved in this process.

Acknowldgments: The authors thank D. Roth, R. Wang and H. Tran from NRC-IMS, as well as C. Adams, R. VanDusen and R. Adams from the Carleton University Microfabrication facility. Additionally, they acknowledge NSERC and the NRC-GSSSP programme for their financial support. F. Semond, a visiting researcher at NRC-IMS, thanks the DGA/D4S/MRIS for financial support.

© National Research Council of Canada 2010 10 November 2009

doi: 10.1049/el.2010.3167

One or more of the Figures in this Letter are available in colour online.

P.N. Chyurlia and N.G. Tarr (Department of Electronics, Carleton University, 1125 Colonel By Drive, Ottawa, Ontario K1S 5B6, Canada) E-mail: chyurlia@doe.carleton.ca

- T. Lester, J.A. Bardwell, S. Rolfe and H. Tang (National Research Council of Canada: Institute for Microstructural Sciences, 1200 Montreal Road, Ottawa, Ontario K1A 0R6, Canada)

- F. Semond (CNRS-CHREA, rue Bernard Gregory 06560, Valbonne, France)

#### References

- Kasper, E., Herzog, H.J., and Woerner, K.: 'Monolithic integration using differential Si-MBE', J. Cryst. Growth, 1987, 81, pp. 458–462

- 2 Matsunaga, K., Tanomura, M., and Nakayama, T.: 'Analogue dynamic supply voltage L-band GaN high power amplifier with improvement on efficiency and linearity'. Microwave Symposium 2007. IEEE/MTT-S International, Honolulu, HI, USA, June 2007, pp. 1107–1110

- Pearton, S.J., Kang, B.S., and Chu, S.N.G.: 'GaN-based diodes and transistors for chemical, gas, biological and pressure sensing', *J. Phys., Condens. Matter*, 2004, 16, R961–R994

Faucher, M., Grimbert, B., and Theron, D.: 'Amplified piezoelectric

- 4 Faucher, M., Grimbert, B., and Theron, D.: 'Amplified piezoelectric transduction of nanoscale motion in gallium nitride electromechanical resonators', *Appl. Phys. Lett.*, 2009, **94**, (23), id. 233506

- 5 Chung, J.W., Lee, J.-K., Piner, E.L., and Palacios, T.: 'Seamless on-wafer integration of Si(100) MOSFETs and GaN HEMTs', *IEEE Electron Device Lett.*, 2009, 30, (10), pp. 1015–1017

- 6 Chyurlia, P., Semond, F., Lester, T., and Tarr, N.G.: 'Windowed growth of AlGaN/GaN heterostructures on silicon ⟨111⟩ substrates for future MOS integration', *Phys. Status Solidi A*, 2009, 206, (2), pp. 371–374

- 7 Germain, M.: 'IMEC enlarges nitride epiwafers', Compound Semicond., December 2008, pp. 23–25

- 8 Bardwell, J.A., Haffouz, S., Kochtane, A., Lester, T., Storey, C., and Tang, H.: 'AIGaN/GaN HFETs fabricated from maskless selectively grown mesas on Si(111) substrates', *Electron. Lett.*, 2007, **43**, (22), pp. 1230–123

- 9 Miller, M.A., and Mohney, S.E.: 'V/Al/V/Ag ohmic contacts to n-AlGaN/GaN heterostructures with a thin GaN cap', Appl. Phys. Lett., 2007, 91, (1), p. 012103

- 10 Cordier, Y., Moreno, J.-C., and Semond, F.: 'Demonstration of AlGaN/GaN high-electron-mobility transistors grown by molecular beam epitaxy on Si(110)', *IEEE Electron Device Lett.*, 2008, 29, pp. 1187–1189